It is not too late to learn FPGA: Getting Started with programmable logic

Countless tutorials and books’ chapters introduce the technology itself and the theory behind it or behind other programmable logic chips like CPLD. Thus, there is no intention to duplicate the efforts. Instead, this article is a practical jump-in with real tools with a mention of theoretical terms when needed.

This article will be good for anyone looking to know how real FPGA works. It will be more about Xilinx as the used development kit has a Xilinx chip.

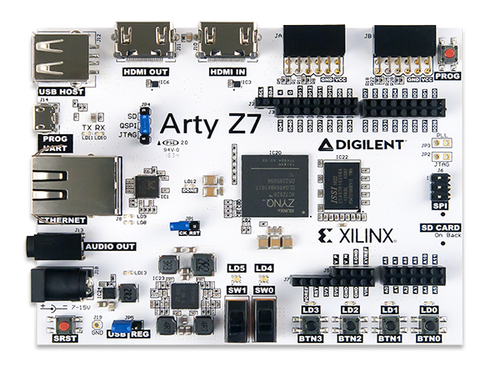

The Used Hardware

The $170-$200 Arty Z7 board from Digilent contains an FPGA chip XC7Z010-1CLG400C which is part of the Zynq-7000 family from Xilinx. Knowing that XC7Z010-1CLG400C unit price on DigiKey is around $114 explains why usually most development boards around FPGA chips are way more expensive than MCU ones; The FPGA chip itself is expensive!

This board contains, in addition to the FPGA chip, the following:

A: IS43TR16256A-125KBL a 512MB DDR3 memory connected to the hard memory controller in the Processor Subsystem (PS) contained in Zynq-7000 family.

B: S25FL128SAGMFI000 a 16MB NOR Flash to be used to initialize the Processor Subsystem (PS) subsystem as well as to configure the Programmable Logic (PL) subsystem.

C: FT2232HQ a configurable multi-purpose dual-channel USB bridge, one channel for USB-UART and the other for USB-JTAG communication for debugging and programming.

D: USB3320C a Physical transceiver to one of the two available PS USB OTG interfaces on the FPGA chip.

E: RTL8211E-VL a Physical transceiver to implement a 10/100/1000 Ethernet port for network connection.

F: TXS02612 a voltage level shifter between an MicroSD card and the FPGA.

Board schematic can be found at Digilent website.

The Zynq-7000 family is an SoC that integrates together a processing system (PS) and Xilinx programmable logic (PL) in a single device. Namely, the XC7Z010/20, the FPGA part inside Arty Z7, has Dual ARM Cortex A9 for Processor Subsystem (PS) and Artix®-7 FPGA for Programmable Logic Subsystem (PL).

Having a processing system and programmable logic in the same chip allows the developer to put non-critical tasks on the PS part and the critical ones on the PL side. Keep in mind that you can also use the PL part to implement a soft processor core like MicroBlaze.

MicroBlaze is the Xilinx’s free soft processor core, optimized for embedded applications on Xilinx devices.

The unit that expresses how big the FPGA chips, programmable logic (PL) speaking, is Configurable Logic Block (CLB). In Zynq-7000, each CLB consists of 2 sub-parts called “Slices“. Each slice consists of 6-input Look-up Tables (LUTs) and eight storage elements.

Any logic design is basically will be implemented using these CLBs with programmable interconnections. In total, each CLB In Zynq-7000 has the following elements:

Here is how Slices are connected inside the CLB:

The detailed diagram of each Slice is demonstrated below:

The total number of CLB and logical elements the XC7Z010 has are presented in the following table:

To give an example of how these numbers are big, we can check how much Logic cells it takes when one Microblaze soft processor is used in Z-7007S FPGA with 23K logic cell.

The FPGA is like any other embedded unit, it needs to interact with the physical world and capture or sense electrical signals. To that end, The 7 series FPGAs offer both high-performance (HP) and high-range (HR) I/O types. Although, XC7Z010-1CLG400C has only HR type.

The following table shows the difference between both types:

The FPGA I/O are available for both processing system (PS) and programmable logic (PL) and the following table shows the available I/O for the used package XC7Z010-1CLG400C.

Now, it is time to see the general architecture of Zynq-7000 SoC chips.

After this introduction, we got a very rough image of what is inside the FPGA chip and the development board that we are going to deal with in the next practical examples.

The Used Software

Xilinx provides a Software Suite called Vivado . The design flow in the Vivado Design Suite is shown in the following chart.

Vivado has tools for each step in the design flow or link to 3rd party tools. It is early to get into each design step in detail as some will be shown step-by-step in the examples.

In case the FPGA design uses a Microblaze soft processor, then there is a need to use Vitis IDE from Xilinx for software development of embedded code runs on Microbalze. Vitis is a tool that combines all aspects of Xilinx® software development into one unified environment.

Xilinx provides the PetaLinux tools set which is an Embedded Linux System Development Kit. It offers a full Linux distribution as well as a complete configuration, builds, and deploys the environment for Xilinx silicon. PetaLinux contains Yocto Extensible SDK and it will be used to build the following: FSBL – U-BOOT – ARM Trusted Firmware – Linux – Libraries and applications.

Example #1: A Switch and An LED

You need first to add the needed files that define Digilent boards to Vivado in order to use them during project creation. The added files are basically XML files defining different interfaces on the board. Interfaces such as Slide Switches, Push Buttons, LEDs, USB-UART, DDR Memory, Ethernet etc

The steps of adding Digilent files are shown in the recording:

Now, it is time to open Vivado IDE and create a project and specify our board (Arty Z7) while project creation.

The program in this example will be extremely simple and written in Verilog language.

module top(

input wire clk,

output reg [1:0] led,

input wire [1:0] sw

);

always @ (posedge clk)

begin

if(sw[0] == 0)

begin

led[0] <= 1'b0;

end

else

begin

led[0] <= 1'b1;

end

end

endmodule

The thing that makes the symbols like clk, led and sw known in the compilation is called Xilinx Design Constraints (XDC). This file will map symbols to their physical meaning. For example the flowing line:

set_property -dict { PACKAGE_PIN M20 IOSTANDARD LVCMOS33 } [get_ports { sw[0] }];

It specifies the pin number of SW0 and the IO type. The constraints files for Digilent’s board are available on Github.

The official general definition of Design constraints is: “ define the requirements that must be met by the compilation flow in order for the design to be functional on the board.”

By writing the code in Verilog which is a hardware description language (HDLs), the design stage is finished. This is called in digital circuit design register-transfer level (RTL) defined in Wikipedia as the following: “RTL is a design abstraction which models a synchronous digital circuit in terms of the flow of digital signals (data) between hardware registers, and the logical operations performed on those signals.“

The example code is yet simpler than the definition. But, if we’re going to map the current stage to the Design Flow, it will match the ‘RTL Development’ stage.

The next important stage is ‘Synthesis’ which is defined in Vivado user guide UG901 by the following: “ Synthesis is the process of transforming an RTL-specified design into a gate-level representation”. In other words, it will convert the design to a net-list of connected FPGA logic gates. It is an implementation from RTL to a logic design.

Now it is the turn of ‘Implementation’ which includes all steps necessary to place and route the netlist ( the outcome of Synthesis step) onto device resources.

The last step is to generate what is called Bitstream which is the file that will be loaded/programmed to the FPGA.

All steps are shown in this recording:

Example #2: Ready Made IP

In this example, a Microblaze soft processor will be added to the design as a ready IP block. This will add a need to write a code to run inside the processor. There are few steps to be done in Vivado in order to export the files that are going to be used in Vitis IDE to write the embedded software. Later on, the compiled embedded software will be merged to the Bitstream file that contains the IP blocks. The final file will then be programmed to the FPGA.

Using “IP Integrator-> Create Block Design”, we will add the Microblaze IP and all other peripherals like GPIO. All IP blocks in the design will communicate using the AXI interface. AXI is part of ARM AMBA bus. To read more about this bus you can refer to AXI Reference Guide UG761. Even the GPIO will have a block called AXI GPIO that provides a general purpose input/output interface to AXI.

The steps of build this soft code is shown in this recording:

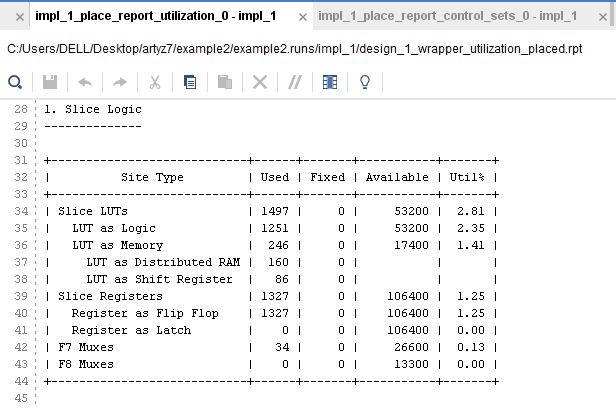

The utilization of the FPGA resources are shown in one of the produced reports in Vivado as the following:

The device with Microblaze inside will look like the following:

The final block design is shown below. You can mention the Memory block, clock block, AXI block for GPIO, and the Micobalze block with debugging block and interrupt controller block.

To read/learn more about Microblaze, it is advised to check Element14 Lab 2 in one of their workshops.

Conclusion

XC7Z010 and Zynq 7000 family may not be the best family to start with your journey with FPGA due to the complexity added from having 2 parts inside the same chip, PL part, and PS part. Many lower-end families may be more suitable like Spartan-3AN and Spartan 6 which contains only FPGA inside, but it is still not bad to have Arty Z7 board from Digilent for the first time especially if you don’t want to buy again a costly FPGA development boards each time you go higher with applications and also if you are already interested in such programmable SoC. However, you may take a look at the great Joel Williams comparison tables between different FPGA boards across different designers and different FPGA manufacturers.

This article introduced very roughly what is inside XC7Z010/20 using Arty Z7 board from Digilent and we worked on 2 simple examples to go through the design steps. FPGA has details way beyond this article and courses like Introduction to FPGA Design for Embedded Systems on Coursera can give thoughts on these details like how to design logic with timing constraints and how to avoid any violations or how to optimize the design in terms of resources and power. However, this course is designed around Quartus Prime suite and Altera mainly, but the concepts are still similar.

In the next part, we will look more at the PS part of XC7Z010/20 as this part was mostly about the PL part. Moreover, we should see how to run Linux on Arty Z7 and what it takes to do so.

References

Xilinx Zynq Technical Reference Manual

The well-written 3 parts tutorial by Time to Explore.

7 Series FPGAs CLB User Guide.

7 Series FPGAs SelectIO Resources User Guide.

Vivado System-Level Design Flows (UG892).

Vivado Design Suite User Guide: Embedded Processor Hardware Design (UG898).

Great! Looking forward for the next sequel.

Best regards!

Tom

Thanks Tom.

Sure, As soon as possible