لم تتأخر عن تعلّم الـFPGA: مقدّمة إلى المنطق المُبرمَج Programmable Logic

لن يكرر المقال الجهود الموجودة في عدد غير محصور من المقالات الأخرى والكتب والدورات التي تشرح عن التقنية FPGA بحد ذاتها وإنما سيكون قفزة عمليّة إلى الأدوات الحقيقيّة المستخدمة مع إشارة للمفاهيم العلميّة عند الحاجة لها. لذلك ستكون المقالة مناسبة لكل من يبحث عن كيفية عمل الـFPGA عمليّاً ولا سيما لشرائح شركة Xilinx.

قبل البدء … يمكن للقارئ الاطلاع على اللقاء وجلسة الأسئلة والأجوبة لعتاديات مع أحد خبراء الـFPGA وأيضاً قراءة المقال التأسيسي المنشور سابقاً مصفوفة البوابات المنطقية القابلة للبرمجة FPGA: مقدمة.

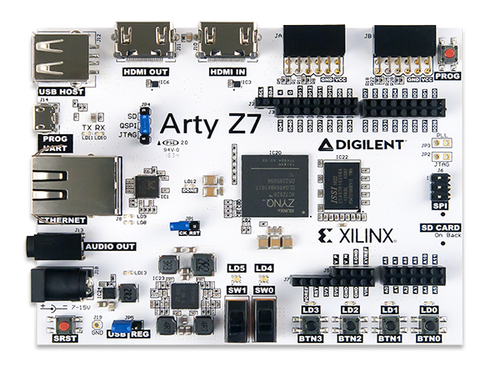

العتاد المستخدم

سنستخدم في هذا المقال دارة من شركة Digilent تسمى Arty Z7 board والتي تحوي شريحة XC7Z010-1CLG400C وهي تنتمي لعائلة Zynq-7000. بمعرفة سعر هذه الشريحة لوحدها من موقع مثل DigiKey والبالغ $114يفسّر لماذا هذه الدارة غالية نسبيّاً (حوالي $170-$200 ) ولماذا هي أغلى من دارات المتحكمات الصغريّة، وذلك لأن الشريحة بحد ذاتها غالية.

تحوي هذه الدارة بالإضافة إلى شريحة الـ FPGA

- A: شريحة IS43TR16256A-125KBL ذاكرة من نوع DDR3 بسعة 512MB موصولة مع متحكم الذاكرة الموجود في قسم المعاجلة Processor Subsystem (PS) subsystem المتوفر في عائلة Zynq-7000.

- B: شريحة S25FL128SAGMFI000 ذاكرة من نوع NOR Flash بسعة 16MB وتستخدم لتهيئة قسم المعالجة Processor Subsystem (PS) subsystem وقسم المنطق Programmable Logic (PL) subsystem أيضاً.

- C: شريحة FT2232HQ وهي دارة تحويل اتصال مع اليو إس بي قابلة للضبط متعّددة الأقنية، تتوفر فيها قناة للاتصال USB-UART وقناة USB-JTAG.

- D: شريحة USB3320C وهي دارة مواءمة اتصال فيزيائي مع اليو إس بي Physical transceiver تستخدم مع منافذ الـOTG المتوفّرة في الشريحة FPGA.

- E: شريحة RTL8211E-VL وهي دارة مواءمة اتصال فيزيائي مع Physical transceiver للإيثرنيت Ethernet.

- F: شريحة TXS02612 وهي شريحة مواءمة مستويات جهود بين الـFPGA وكرت الذاكرة MicroSD card.

- المزيد من التفاصيل موجودة في مخطط الدارة المتوفر في موقع Digilent.

يتوفر في عائلة Zynq-7000 قسمين وهما processing system واختصاراً PS و programmable logic واختصاراً PL وتحوي شريحة XC7Z010 بالتحديد على نواتين ARM Cortex A9 تشكلان القسم PS و Artix®-7 FPGA يمثل قسم الـ PL.

إن وجود قسم منطقي وقسم معالجة في الشريحة نفسها يوفّر للمطور إمكانية وضع جزء التصميم الحساس لسرعة التنفيذ في القسم المنطقي والجزء الأقل حساسيّة في قسم المعالجة. بالرغم من توفر معالجين في قسم المعاجلة إلا أنه يمكن أيضاً تضمين معالجات إضافية في القسم المنطقي مثل المتحكم المنطقي البرمجي MicroBlaze.

إن MicroBlaze هو نواة معالج (برمجي Soft) من تصميم Xilinx مجاني ومخصّص للتطبيقات المضمّنة على أجهزة Xilinx.

إن الوحدة التي تستخدم عادة للتعبير عن كِبَر شريحة FPGA، من الناحية المنطقيّة، هي Configurable Logic Block (CLB) أو الكتل المنطقية القابلة للضبط وتتألف كل كتلة في Zynq-7000 من جزأين وتسمى كل جزء شريحة أو Slices وكل شريحة تتكون من جدول تقابل ذو 6 مداخل 6-input Look-up Tables (LUTs) وثمانية عناصر تخزين. يتألف أي تصميم منطقي من CLBs متصلة مع بعضها البعض.

تتصل الشرائح Slices داخلياً في الكتلة CLB كما يظهر:

إن المخطط التفصيلي لمحتوى كل شريحة Slice هو:

إن العدد الكلي للكتل المنطقيّة في الشريحة XC7Z010 والموارد المنطقيّة الأخرى مذكورة في الجدول التالي:

ولكي نتخيل هذه الأرقام كم هي كبيرة فإن معرفة عدد الخلايا المنطقية التي تتطلبها تمثيل معالج Microblaze في شريحة Z-7007S ذو ال23 ألف خلية يعطي صورة واضحة لضخامة الموارد المتوفّرة:

وكأي نظام مضمّن فإن الـFPGA تتواصل مع العالم الفيزيائي المحيط وتتلقى أو تصدر الإشارات الكهربائية عبر أرجل الدخل والخرج I/O. لذلك توفر هذه العائلة نوعين من المداخل/المخارج وهما high-performance (HP) و high-range (HR) ويتوفّر في الشريحة XC7Z010-1CLG400C النوع HR فقط ويتوفر في الجدول التالية تلخيص لمزايا النوعين HP و HR:

تتوفّر المخارج والمداخل لكلا القسمين المنطقي PL والمعالجة PS ويظهر في الجدول التالي المداخل/المخارج المتوفرة في الشريحةXC7Z010 ذات نوع 1CLG400C:

وبعد هذه المقدّمة يمكن الاطلاع على البنية العامّة الموجودة داخل الشرائح من عائلة Zynq-7000 :

إلى هنا يمكن رسم صورة بسيطة عن مكونات هذه الشريحة واللوحة التطويرية المستخدمة في المثالين القادمين.

البرنامج المستخدم

توفّر Xilinx أداة برمجيّة تسمى Vivado ويوضّح المخطط التالي مراحل التصميم design flow في البرنامج.

يتوفّر لكل مرحلة أداة في Vivado ومن المبكّر الدخول في تفاصيل كل مرحلة حيث سيتم توضيح بعضها في الأمثلة اللاحقة.

في حالة استخدام معالج Microblaze فإنه يتوجب استخدام بيئة التطوير المتكاملة Vitis لكتابة الكود المضمّن الذي سيُنفّذ على المعالج. إن Vitis يتضمّن كل الأدوات اللازمة لتطوير البرنامج في بيئة موحّدة.

في حال الرغبة في استخدام نظام تشغيل Linux على الشريحة فإن أدوات PetaLinux متوفّرة لإصدار نسخة Linux مهُيْئة ومخصصة للعمل على شريحة Xilinx ويحتوي PetaLinux على Yocto Extensible SDK والذي سيستخدم لبناء كل من: FSBL – U-BOOT – ARM Trusted Firmware – Linux – Libraries – applications.

المثال الأول: مفتاح وليد ضوئي

ستحتاج في البداية إلى إضافة بعض الملفّات التي تجعل دارات شركة Digilent متوفّرة في Vivado عند إنشاء المشاريع. إن الملفات المضافة هي بشكل أساسي XML والتي تحدد الطرفيات في الدارات مثل Slide Switches, Push Buttons, LEDs, USB-UART, DDR Memory, Ethernet … إلخ

إن الخطوات اللازمة لإضافة الملفات موضّحة في التسجيل التالي:

والآن لنقم بفتح البرنامج Vivado وإنشاء مشروع مع تحديد الدارة Arty Z7 أثناء إنشاء المشروع.

إن البرنامج المستخدم في هذا المثال بسيط ومكتوب بلغة Verilog

module top(

input wire clk,

output reg [1:0] led,

input wire [1:0] sw

);

always @ (posedge clk)

begin

if(sw[0] == 0)

begin

led[0] <= 1'b0;

end

else

begin

led[0] <= 1'b1;

end

end

endmodule

إن ما يجعل الرموز clk, led , sw معرّفة أثناء ترجمة البرنامج هو ما يسمى ملف Design Constraints (XDC) وهو ملف يربط الرموز بمدلولها الفيزيائي. في المثال التالي توضيح:

set_property -dict { PACKAGE_PIN M20 IOSTANDARD LVCMOS33 } [get_ports { sw[0] }];

يحدد السطر السابق الرجل المتصل بها SW0 نوع هذا الدخل/الخرج. يتوفّر الملف الكامل XDC لدارات Digilent على غيت هب.

تعد مرحلة التصميم منتهية بكتابة الكود بلغة Verilog وهي أحد لغات تعليم الآلة hardware description language (HDLs) وهذا يُسمى في تصميم الدارات المنطقية بالتصميم register-transfer level (RTL) وتم تعريفه في ويكيبيديا بالتالي:”هو تصميم مجرّد يمثّل دارة رقميّة متزامنة synchronous digital circuit يعبّر عنها بتمثيل شكل دفق الإشارات الرقميّة (البيانات) في السجلات العتادية hardware registers والعمليات المنطقية المطبّقة على هذه الإشارات”.

قد يكون برنامج المثال أبسط من التعريف بحد ذاته ولكن لو أردنا أن نقابل هذه المرحلة بمقابلها من المخطط Design Flow فهو يقابل مرحلة ‘RTL Development’ .

إن المرحلة المقبلة هي التركيب ‘Synthesis’ والذي تم تعريفه في الدليل Vivado user guide UG901 بأنه العملية التي تحويل التصميم من مستوى RTL إلى تصميم على مستوى البوابات المنطقيّة وبكلمات أخرى هو تحويل التصميم إلى net-list من البوابات المنطقيّة المتصلة.

تسمى العمليّة التي يتم فيها تخطيط كيفيّة توضيع هذا التصميم على الموارد الفعليّة المتوفرة في الشريحة وكيفية التوصيل بينها بعملية التنفيذ ‘Implementation’ . الخطوة الأخيرة هي بناء ملف يسمّى Bitstream وهو الملف الذي سيتم تحميله/برمجته على الـFPGA.

إن الخطوات اللازمة في هذا المثال موضّحة في التسجيل التالي:

المثال الثاني: استخدام تصميم IP جاهز

في هذا المثال سوف نستخدم المتحكم البرمجي Microblaze وسنقوم بإضافته ككتلة جاهزة إلى التصميم، وبهذا فنحن بحاجة إلى كتابة الكود المضمّن باستخدام Vitis IDE وذلك بعد مجموعة من الخطوات التي يجب اتباعها لتصدير المشروع من Vivado إلى Vitis. سيتم دمج مخرجات ترجمة البرنامج المضمّن ودمجها مع ملف الـBitstream الذي حصلنا عليه مسبقاً من Vivado ليتم برمجة الملف النهائي إلى الشريحة.

سنقوم باستخدام الأداة IP Integrator-> Create Block Design وذلك لإدراج التصاميم IP وتحديداً Microblaze والطرفيات الأُخرى متل المداخل/مخارج GPIO. إن كل الكتل ستتواصل مع بعضها باستخدام AXI وهو جزء من الناقل ARM AMBA وللقراءة أكثر عن هذا الناقل يمكن الاطلاع على الدليل المرجعي AXI Reference Guide UG761. إن المداخل والمخارج ستكون عبارة عن كتلة block وذلك لتوفير تواصل باستخدام AXI مع أرجل المنافذ.

في الفيديو أدناه تطبيق للخطوات اللازمة في هذا المثال:

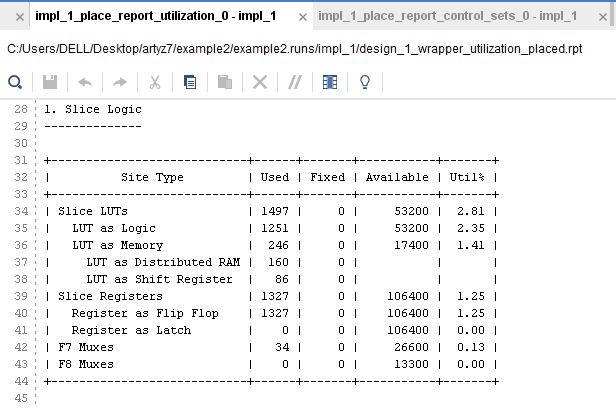

يظهر في الجدول التالي في أحد التقارير الناتجة في Vivado ويظهر الموارد المستهلكة في هذا المثال:

يظهر في الشكل التالي ما تبدو عليه داخل الشريحة لتمثيل المعالج:

إن المخطط النهائي block design يظهر في الأسفل. يمكن ملاحظة كتلة الذاكرة وكتلة الدخل/خرج وكتلة المعالج Micobalze وملحقاته مثل متحكم المقاطعات وكتلة التنقيح.

للاطلاع أكثر، يُنصح بتابعة تسجيل القسم الثاني من أحد الورشات المقدّمة من Element14 وهو بناء MicroBlaze.

تلخيص

قد لا يكون XC7Z010 والعائلة Zynq 7000 هي الأنسب للبدء في عالم FPGA نظراً للتعقيد الذي أضافته وجود جزء منطقي وآخر معالجة داخل الشريحة الواحدة. حيث يتوفّر شرائح من عوائل منخفضة مثل Spartan-3AN أو Spartan 6 تحوي على جزء منطقي فقط ولكن ومع ذلك قد تكون فكرة اقتناء دارة مثل Arty Z7 من شركة Digilent فكرة سديدة في حالة عند الرغبة بشراء دراة تطويريّة جديدة مع تطور مهاراتك أو في حال الاهتمام في فكرة الدمج الموجودة بين المكون المنطقي والمعالج في شريحة واحدة. يمكن الاطلاع على جداول مقارنة بين أنواع مختلفة لمصممين مختلفين باستخدام شرائح مختلفة مع أسعارها.

كان هذا المقال مقدّمة بسيطة للغاية عما يوجد داخل شريحة XC7Z010/20 باستخدام دارة Arty Z7 وتم العمل على مثالين لتوضيح خطوات التصميم. إن الـFPGA ذو تفاصيل كثيرة وعميقة أبعد مما تم تغطيته في هذا المقال ويُنصح للمهتمين بحضور الدورة على منصة كورسيرا Introduction to FPGA Design for Embedded Systems والتي تعطي تصوّر عن هذه التفاصيل مثل كيفية التصميم مع الأخذ بعين الاعتبار التقييدات الزمنية timing constraints للتصميم وكيفية عدم انتهاكها وكيفية تحسين التصميم من ناحية الأداء من ناحية الموارد ومن ناحية الطاقة. على الرغم من أن الدورة مصممة حول برنامج Quartus Prime وشركة Altera إلا أن المفاهيم تبقى متشابهة.

سوف نتحدّث في الجزء الثاني أكثر عن جزء المعالجة PS في الشريحة XC7Z010/20 وكيفيّة تشغيل نظام Linux عليها وماذا يحتاج ذلك.

المراجع

- Xilinx Zynq Technical Reference Manual

- Arty-S7 Workshop by Element14

- Time to Explore Arty Series.

- Arty Z7 Reference Manual

- Arty Z7 Schematic

- Xilinx Zynq Datasheet

- 7 Series FPGAs CLB User Guide.

- 7 Series FPGAs SelectIO Resources User Guide.

- Vivado System-Level Design Flows (UG892).

- Vivado Design Suite User Guide: Embedded Processor Hardware Design (UG898).